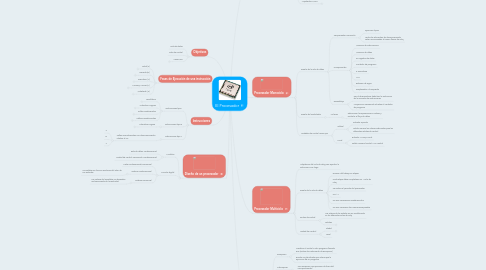

1. Objetivos

1.1. Ruta de datos

1.2. Ruta de control

1.3. nanoMIPS

1.3.1. Arquitectura MIPS simplificada

2. Fases de Ejecución de una instrucción

2.1. Fetch (F)

2.1.1. Busca en memoria la instrucción apuntada por el PC.

2.2. Decode (D)

2.2.1. Decodificación de la isntrucción, separar los diferentes campos.

2.3. Execution (X)

2.3.1. Ejecución de la operación por opcode

2.4. Memory Access (M)

2.4.1. Accede a la memoria para leer o escribir

2.5. Writeback (W)

2.5.1. Vuelca un resulatdo a un registro

3. Diseño de un procesador

3.1. Módulos

3.1.1. Ruta de datos: combinacional

3.1.2. Unidad de control: secuencial o combinacional

3.2. Circuito digital

3.2.1. Parte combinacional+secuencial

3.2.2. Sistema combinacional

3.2.2.1. Sus salidas son función exclusiva del valor de sus entradas

3.2.3. Sistema secuencial

3.2.3.1. Los valores de las salidas no dependen exclusivamente de las entradas

4. Instrucciones

4.1. Instrucciones tipo I

4.1.1. Load/Store

4.1.1.1. F

4.1.1.2. D

4.1.1.3. X

4.1.1.4. M

4.1.1.5. W

4.1.2. Aritmético-Lógicas

4.1.2.1. F

4.1.2.2. D

4.1.2.3. X

4.1.2.4. W

4.1.3. Saltos condicionales

4.1.3.1. F

4.1.3.2. D

4.1.3.3. X

4.1.4. Saltos incondicionales

4.1.4.1. F

4.1.4.2. D

4.1.4.3. X

4.2. Instrucciones tipo R

4.2.1. Aritmético Lógicas

4.2.1.1. F

4.2.1.2. D

4.2.1.3. X

4.2.1.4. W

4.3. Instrucciones tipo J

4.3.1. Saltos incondicionales con direccionamiento relativo al PC

4.3.1.1. F

4.3.1.2. D

4.3.1.3. X

5. Procesador Secuencial

5.1. Mientras no termine una instrucción no comienza la siguiente

5.2. Procesador monociclo

5.2.1. Cada instrucción se completa en un único ciclo de reloj

5.2.2. CPI=1

5.2.3. La duración del ciclo de reloj es el de la instrucción que más tarda en ejecutarse

5.3. Procesador multiciclo

5.3.1. Cada instrucción puede tardar más de un ciclo en ejecutarse

5.3.2. CPI > 1

5.3.3. La duración de un ciclo es de la duración de la etapa más larga

5.4. nanoMIPS

5.4.1. Repertorio de instrucciones

5.4.1.1. Acceso a memoria: LW, SW

5.4.1.2. Operaciones aritmético-lógicas: ADD, SUB, AND, OR, SLT

5.4.1.3. Control de flujo: BEQ

5.5. Metodología para el diseño

5.5.1. Paso 1: Analizar el repertorio de instrucciones

5.5.2. Paso 2: Establecer la metodología de temporización

5.5.3. Paso 3: Seleccionar el conjunto de módulos

5.5.4. Paso 4: Ensamblar la ruta de datos localizando los puntos de control

5.5.5. Paso 5: Determinar los valores de los puntos de control

5.5.6. Paso 6: Diseñar la lógica de control

5.5.7. Paso 5: Determinar los valores de los puntos de control

5.6. Arquitectura MIPS

5.6.1. Formato de la instrucción

5.6.1.1. Todas las instrucciones de MIPS32 tienen 32 bits de anchuta y 3 tipos de instrucciones: I, R, J

5.6.2. Subconjunto

5.6.2.1. Instrucciones con referencia a memoria (Tipo I)

5.6.2.2. Instrucciones aritmético-lógicas con operandos en registros (Tipo R)

5.6.2.3. Instrucciones de dalto condicional (Tipo I)

6. Procesador Monociclo

6.1. Diseño de la ruta de datos

6.1.1. Temporizador monociclo

6.1.1.1. Ejecución típica

6.1.1.2. Todos los elementos de almacenamiento están sincronizados al mismo flanco de reloj

6.1.2. Componentes

6.1.2.1. Memoria de instrucciones

6.1.2.2. Memoria de datos

6.1.2.3. 32 registros de datos

6.1.2.4. Contador de programa

6.1.2.5. 2 sumadores

6.1.2.6. ALU

6.1.2.7. Extensor de signo

6.1.2.8. Desplazador a la izquierda

6.1.3. Ensamblaje

6.1.3.1. Para la búsqueda se debe leer la isntrucción de la memoria de instrucciones

6.1.3.2. La ejecución secuencial actualiza el contador de programa

6.2. Diseño del controlador

6.2.1. La tarea

6.2.1.1. Seleccionar las operaciones a realizar y controlar el flujo de datos

6.3. Unidades de control nanoMips

6.3.1. Global

6.3.1.1. Entrada: opcode

6.3.1.2. Salida: Genera los valores adecuados para las diferentes señales de control

6.3.2. Local

6.3.2.1. Entrada: ALUOp, Funct

6.3.2.2. Salida: Genera la señal ALU Control

7. Procesador Multiciclo

7.1. Adaptación del ciclo de reloj para ejecutar la instrucción más larga

7.2. Diseño de la ruta de datos

7.2.1. División del trabajo en etapas

7.2.2. Cada etapa debe completarse en 1 ciclo de reloj

7.2.3. Se reduce el periodo del procesador

7.2.4. CPI > 1

7.2.5. No son necesarios sumadores extra

7.2.6. No son necesario dos memorias separadas

7.3. Puntos de control

7.3.1. Los valores de las señales se van modificando en los diferentes ciclos de reloj

7.3.2. Señales

7.3.2.1. lorD

7.3.2.2. MemRead

7.3.2.3. MemWrite

7.3.2.4. MemToReg

7.3.2.5. RegDst

7.3.2.6. RegWrite

7.3.2.7. ALUSrcA

7.3.2.8. ALUSRcB

7.3.2.9. ALUOp

7.3.2.10. PCSrc

7.3.2.11. PCWrite

7.3.2.12. PCWriteCond

7.3.2.13. IRWrite

7.4. Unidad de Control

7.4.1. Global

7.4.1.1. Circuito Secuencial

7.4.1.2. Entrada opcode

7.4.1.3. Maquina de estados

7.4.1.3.1. Llamada cableada

7.4.1.3.2. 8 estados que se ejecutan en un máximo de 5 ciclos

7.4.1.3.3. Cuando se modifica una instrucción se debe rediseñar toda la unidad de control

7.4.1.4. Microprograma

7.4.1.4.1. Memoria ROM

7.4.1.4.2. Codificación Horizontal

7.4.1.4.3. Codificación vertical

7.4.1.4.4. Unidades de control

7.4.2. Local

8. Excepciones

8.1. Excepción

8.1.1. Transferir el control a otro programa llamado RTE (Rutina de Tratamiento de Excepción)

8.1.2. Evento no planificado que interrumpe la ejecución de un programa

8.2. Interrupción

8.2.1. Una excepción que proviene de fuera del microprocesador

8.3. Tipos

8.3.1. Interrupciones de E/S

8.3.2. Llamadas al Sistema Operativo

8.3.3. Puntos de ruptura

8.3.4. Código de operación inválidos

8.3.5. Overflow o desbordamiento en la ALU

8.3.6. Fallos de página

8.3.7. Accesos a memoria no alineados

8.3.8. Violación de zonas protegidas de memoria

8.3.9. Fallos de Hardware

8.3.10. Fallos de alimentación

8.4. Componentes

8.4.1. Registro Exception

8.4.2. EPC (Contador de Programa Excepción)

8.4.3. Restador

8.5. Señales de control

8.5.1. ALU_overflow

8.5.2. Ilegal_opcode

8.5.3. Exception

8.5.4. ExceptionWrite

8.5.5. EPCWrite

8.5.6. PCWrite

8.6. Unidades de control

8.7. Unidades de control en nanoMIPS

8.7.1. Monociclo

8.7.1.1. Sólo añadir las nuevas señales al circuito combinacional

8.7.2. Multiciclo

8.7.2.1. Modificar la máquina de estados