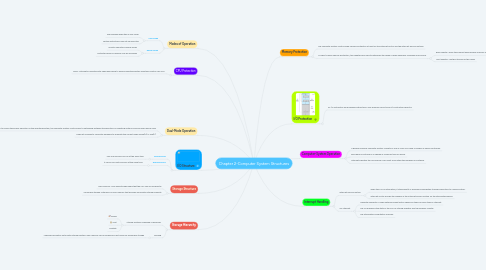

1. I/O Structure

1.1. Synchronous

1.1.1. only one process can run at the same time.

1.2. Asynchronous

1.2.1. It can be run multi-process at the same time.

2. Storage Structure

2.1. Main memory- only large storage media that the CPU can access directly

2.2. Secondary storage- extension of main memory that provides nonvolatile storage capacity

3. Storage Hierarchy

3.1. Storage systems organized in hierarchy.

3.1.1. Speed

3.1.2. Cost

3.1.3. Volatility

3.2. Caching

3.2.1. copying information onto faster storage system; main memory can be viewed as a last cache for secondary storage

4. Dual-Mode Operation

4.1. In order to ensure the proper execution of the operating system, the computer system must be able to distinguish between the execution of operating system code and user-define code.

4.2. Mode bit is added to computer hardware to indiacate the current mode: kernel(0) or user(1).

5. Modes of Operation

5.1. User Mode

5.1.1. user program executes in user mode

5.1.2. certain instructions may not be executed

5.2. Kernel Mode

5.2.1. monitor executes in kernel mode

5.2.2. protected areas of memory may be accessed

6. CPU Protection

6.1. Timer- interrupts computer after specified period to ensure operating system maintains control over CPU.

7. Computer-System Operation

7.1. A general-purpose computer system consists of one or more CPUs and a number of device controllers.

7.2. Each device controller is in charge of a specific type of device.

7.3. Interrupt indicates the occurrence of an event from either the hardware or software.

8. Interrupt Handling

8.1. interrupt service routine

8.1.1. When the CPU is interrupted, it stops what it is doing and immediately transfers execution to a fixed location.

8.1.2. Interrupt vector provide the address of the interrupt service routine for the interrupting device.

8.2. OS interrupt

8.2.1. Separate segments of code determine what action should be taken for each type of interrupt.

8.2.2. The OS preserves the state of the CPU by storing registers and the program counter.

8.2.3. The interrupted computation resumes.

9. I/O Protection

9.1. All I/O instruction are privileged instructions; user program cannot issue I/O instructions directly.

10. Memory Protection

10.1. The computer system must provide memory protection at least for the interrupt vector and the interrupt service routines.

10.2. In order to have memory protection, two registers are used to determine the range of legal addresses a program may access

10.2.1. Base register- holds the smallest legal physical memory address.

10.2.2. Limit register- contains the size of the range.