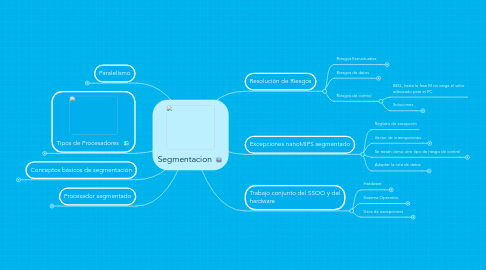

1. Paralelismo

1.1. Arquitecturas alternativas que utilizan varias unidades de procesamiento

1.2. Interno

1.2.1. Un solo CPU, usa la segmentación

1.3. Explícito

1.3.1. Con varias CPUs

1.3.2. SIMD

1.3.2.1. Un solo flujo de instrucciones y múltiples datos

1.3.2.2. Ejemplos

1.3.2.2.1. 3DNow de AMD

1.3.2.2.2. SSE de Intel

1.3.3. MISD

1.3.3.1. Varios flujos de instrucciones y uno solo de datos

1.3.4. MIMD

1.3.4.1. Multiprocesador con varios flujos tanto de instrucciones como de datos

2. Tipos de Procesadores

2.1. Procesadores Secuenciales

2.1.1. PSi no termina de ejecutra una instruccipon no comienza a ejecutar la siguiente.

2.1.2. Procesador Monociclo

2.1.3. Procesador Multiciclo

2.2. Procesadores Segmentados

2.2.1. Permite solapar la ejecución de varias instrucciones

2.2.2. Aprovecha el paralelismo a nivel de instrucción es decir el pipelining

2.3. Encauzamiento

2.3.1. Ejecución de varias instrucciones usando una sola unidad de proceso

2.3.2. Pipeline

2.3.2.1. Dividir una función en subfunciones independientes

2.3.3. Proceso similar a una cadena de montaje

3. Conceptos básicos de segmentación

3.1. CPI=1

3.2. Periodo de reloj limitado por la etapa más lenta

3.3. Diferentes instrucciones tienen que utilizar diferentes recursos

3.4. Problema

3.4.1. Accesos a memoria en las etapas F y M

3.4.2. Acceso a banco de registros en las etapas D y W

3.5. Solución

3.5.1. Se separan las memorias de instrucciones y datos

3.5.2. Multiplexor Etapa F

3.5.3. Restador Etapa X

3.6. Registros de segmentación

3.6.1. Almacenan el resultado de cada etapa al final del ciclo de reloj

4. Procesador segmentado

4.1. Unidad de control

4.1.1. En la etapa D, el opcode permite generar todas las señales de control

4.1.2. Dimensionar los registros de segmentación

4.1.2.1. X

4.1.2.1.1. ALUSrcA, ALUSrcB, ALUOp y RegDest

4.1.2.2. M

4.1.2.2.1. Branch, MemRead y MemWrite

4.1.2.3. W

4.1.2.3.1. MemToReg y RegWrite

4.2. Rendimiento

4.2.1. Productividad aumenta

4.2.1.1. CPI de un procesador secuencial monociclo

4.2.2. Tiempo de ejecución de una única instrucción empeora

4.2.2.1. Periodo de reloj de un procesador multiciclo

4.2.3. Speedup

4.2.3.1. Máximo al segmentar un procesador multiciclo

4.2.3.2. S=tmulticiclo/tsegmentado

4.3. Pipeling vs Paralelismo

4.3.1. Pipelining

4.3.1.1. El HW no está replicado

4.3.2. Arquitecturas paralelas

4.3.2.1. El HW sí está replicado

4.3.3. Juegos de instrucciones para pipelining en MIPS

4.3.3.1. Diseñado para ser ejecutado en un pipeline

4.3.3.2. Diseñado para evitar riesgos en el cause

5. Resolución de Riesgos

5.1. Riesgos Estructurales

5.1.1. Dos o más instrucciones necesitan utilizar el mismo recurso de hardware al mismo tiempo

5.1.2. Resolución

5.1.2.1. Duplicar los recursos de hardware

5.1.2.2. Separar memoria de instrucciones y datos

5.1.2.3. Banco de Registros

5.1.2.3.1. Turnos para leer y escribir

5.1.2.3.2. Escrituras en la primera mitad

5.1.2.3.3. Lecturas en la segunda mitad

5.2. Riesgos de datos

5.2.1. Dos o más instrucciones presentan dependencias de datos entre sí

5.2.2. Tipos de dependencias

5.2.2.1. RAW, Read After Write

5.2.2.2. WAR, Write After Read

5.2.2.3. WAW, Write After Write

5.2.3. Solución software: prevención

5.2.3.1. Reordenar el código

5.2.3.1.1. Responsabilidad del compilador

5.2.3.1.2. Retrasar la ejecución de la instrucción un número K de etapas hasta que desaparezca el problema

5.2.3.2. Sin reordenar las instrucciones

5.2.3.2.1. Insertar instrucciones NOP!

5.2.3.2.2. No requiere de hardware adicional

5.2.4. Mecanismo Hardware

5.2.4.1. Detener el pipeline

5.2.4.1.1. Hardware adicional para detener la actividad en las etapas necesarias del pipeline

5.2.4.1.2. Primero se detecta la dependencia y después se detiene el pipeline

5.2.4.1.3. CPI=Nro Ciclos/ Nro Instrucciones

5.2.4.2. Adelantamiento, data fordwarding

5.2.4.2.1. Pasar el resultado obtenido en una instrucción a las instrucciones

5.2.4.2.2. Identificar todos los adelantamientos

5.2.4.2.3. Adeelantar los operandos a la etapa X

5.2.4.2.4. CPI=Nro Ciclos/Nro Instrucciones

5.2.4.3. Speedup

5.2.4.3.1. S=CPI_sin_adelantamiento/CPI_con_adelantamiento

5.3. Riesgos de control

5.3.1. BEQ, hasta la fase M no carga el valor adecuado para el PC

5.3.2. Soluciones

5.3.2.1. Hardware adicional

5.3.2.1.1. Resolverlo equivale a 3 ciclos de espera

5.3.2.1.2. Reducir a 1 ciclo adelantando la resolución de los datos

5.3.2.1.3. Se obtiene una parada

5.3.2.2. Predicción de salto estática

5.3.2.2.1. salto tomado

5.3.2.2.2. salto no tomado

5.3.2.3. Software: salto retardado, relleno de ranura

5.3.2.3.1. nanoMIPS no modificado, ranura de 3 ciclos

5.3.2.3.2. nanoMIPS modificado, ranura 1 ciclo

6. Excepciones nanoMIPS segmentado

6.1. Registro de excepción

6.2. Vector de interrupciones

6.2.1. Dirección viene determinada por el tipo de excepción

6.2.1.1. Instrucción no definida

6.2.1.2. Desbordamiento aritmético

6.3. Se tratan como otro tipo de riesgo de control

6.3.1. 1. Vaciar el pipeline de instrucciones posteriores a la suma

6.3.2. 2. Carga de instrucciones de la nueva dirección

6.4. Adaptar la ruta de datos

6.4.1. Señal de nuevo valor del PC

6.4.2. Cause Register

6.4.3. Registro de la instrucción de la excepción, EPC

7. Trabajo conjunto del SSOO y del hardware

7.1. Hardware

7.1.1. Detener la instrucción

7.1.2. Completar las instrucciones

7.1.3. Vaciar el pipeline

7.1.4. Guardar la causa de la excepción

7.1.5. Salvar la dirección de la instrucción de la excepción

7.1.6. Saltar a una dirección predeterminada

7.2. Sistema Operativo

7.2.1. Cuando hay desbordamiento el ssoo mata el proceso y retorna el motivo

7.2.2. Cuando es petición de E/S, el ssoo salva el estado del programa

7.3. Usos de excepciones

7.3.1. Manejo de fallos de página y excepciones del TLB