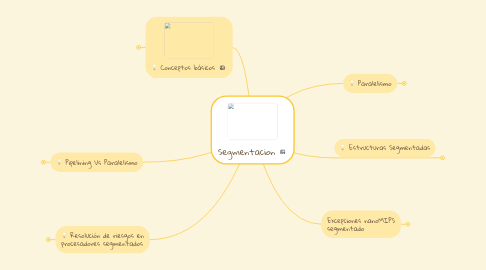

1. Conceptos básicos

1.1. surgió como una técnica para el aumento de prestaciones

1.2. las diferentes instrucciones tienen que utilizar diferentes recursos

1.3. Ejecutando una única instrucción cada vez, el hardware está desaprovechado

1.4. Procesador Segmentado

1.4.1. Ruta de datos NanoMIPS segmentado

1.4.2. Unidad de Control

1.4.2.1. etapa D, el opcode permite generar todas las señales de control necesarias

1.4.2.2. circuito combinacional que genera las señales de control para cada tipo de instrucción a partir del opcode

1.4.3. Rendimiento

1.4.3.1. La productividad aumenta

1.4.3.1.1. CPI=1

1.4.3.2. El tiempo de ejecución de una única instrucción empeora

1.4.3.2.1. Periodo de reloj de un procesador multiciclo

1.4.3.3. Speedup máximo al segmentar un procesador multiciclo

1.4.3.3.1. S = tmulticiclo / tsegmentado

1.4.3.3.2. S = (I•CPI•T)multiciclo / (I•CPI•T)segmentado

2. Pipelining Vs Paralelismo

2.1. Ambas técnicas están orientadas a mejorar el rendimiento

2.1.1. Pipelining

2.1.1.1. El HW no está replicado, sólo está dividido en varias etapas distintas especializadas

2.1.2. Paralelismo

2.1.2.1. El HW sí está replicado por lo que varias operaciones pueden ejecutarse de forma simultánea

3. Resolución de riesgos en procesadores segmentados

3.1. Riesgos Estructurales

3.1.1. dos o más instrucciones necesitan utilizar el mismo recurso hardware al mismo tiempo

3.1.2. Resolución parones estructurales

3.1.2.1. duplicar los recursos hardware, segmentarlos o realizar turnos para acceder a ellos

3.2. Riegos de datos

3.2.1. Dos o más instrucciones presentan dependencias de datos entre sí que podrían llevar a la obtención de resultados erróneos

3.2.1.1. Tipos de dependencias

3.2.1.1.1. RAW

3.2.1.1.2. WAR

3.2.1.1.3. WAW

3.2.2. Solución

3.2.2.1. Software

3.2.2.1.1. Prevencion

3.2.2.2. Hardware

3.2.2.2.1. Detener el pipelining

3.2.2.2.2. Anticipación, data fordwarding

3.3. Riegos de Control

3.3.1. Una instrucción que modifica el valor del PC todavía no lo ha hecho cuando se tiene que comenzar la ejecución de la siguiente instrucción

3.3.2. Solución

3.3.2.1. Hardware adicional

3.3.2.1.1. En la etapa D debemos incluir el hardware

3.3.2.2. Predicción de salto estática

3.3.2.2.1. Intenta evitar esta parada realizando una predicción

3.3.2.3. Software

3.3.2.3.1. Salto retardado, relleno de ranura

4. Paralelismo

4.1. Paralelismo interno

4.1.1. Unica CPU

4.1.1.1. Segmentacion

4.2. Paralelismo Explicito

4.2.1. Varias CPU

4.2.1.1. SIMD

4.2.1.1.1. un solo flujo de instrucciones y múltiples datos

4.2.1.1.2. Ejemplo

4.2.1.2. MISD

4.2.1.2.1. varios flujos de instrucciones y uno solo de datos

4.2.1.3. MIMD

4.2.1.3.1. arquitectura multiprocesador con varios flujo tanto instrucciones como datos

5. Estructuras Segmentadas

5.1. Procesadores Secuenciales

5.1.1. hasta que no termina de ejecutar una instrucción no comienza a ejecutar la siguiente

5.1.1.1. Procesador monociclo

5.1.1.2. Procesador multiclo

5.2. Procesadores Segmentados

5.2.1. permite solapar en el tiempo la ejecución de varias instrucciones

5.2.2. paralelismo a nivel de instruccion, pipelining

5.3. Encauzamiento

5.3.1. Paralelismo implicito

5.3.2. segmentación o pipeline

5.3.2.1. dividir una función en subfunciones independientes

5.3.3. Proceso similar a una cadena de montaje

5.3.4. consigue la ejecución de instrucciones en un tiempo muy inferior a los procesos no encauzados

5.3.5. Ejecución secuencial

5.3.6. dividir las fases de ejecución de las instrucciones en más etapas

5.3.6.1. obtiene un mayor rendimiento

6. Excepciones nanoMIPS segmentado

6.1. se tratan como otro tipo de riesgo de control.

6.2. La ruta de datos se debe adaptar para soportar excepciones

6.3. Métodos para indicar la causa de la excepción

6.3.1. Registro de excepcion

6.3.2. Vector de interrupciones

6.4. Trabajo conjunto del SO y el hardware

6.4.1. Hardware

6.4.2. SO

6.4.2.1. analizar la causa de la excepción y actuar en consecuencia