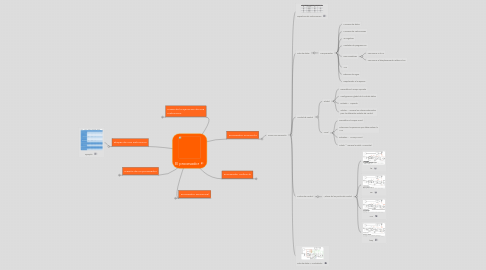

1. Fases de la ejecución de una instrucción

1.1. Fetch (F)

1.1.1. Buscar en memoria la instrucción apuntada por el PC.

1.2. Decode (D)

1.2.1. Decodifica la instrucción

1.3. Execute (E)

1.3.1. Ejecución de la operación indicada en el opcode.

1.4. Memory Access (M)

1.4.1. Si es necesario, accede a la memoria para leer o escribir.

1.5. WriteBack (W)

1.5.1. Si es necesario, se vuelca un resultado a un registro

2. Etapas de una instrucción

2.1. Ejemplo

3. Diseño de un procesador

3.1. Módulos dentro del procesador

3.1.1. Ruta de datos

3.1.2. Unidad de control

3.2. Es un circuito digital que consta de dos partes

3.2.1. Sistema combinacional

3.2.1.1. Sus salidas son función exclusiva del valor de sus entradas

3.2.2. Sistema secuencial

3.2.2.1. Los valores de la salida también dependen del estado anterior o estado interno

3.3. Metodologia

3.3.1. 1. Analizar el repertorio de instrucciones

3.3.2. 2. Establecer la metodología de temporización

3.3.3. 3. Seleccionar el conjunto de módulos

3.3.4. 4. Ensamblar la ruta de datos

3.3.5. 5. Determinar los valores de los puntos de control

3.3.6. 6. Diseñar la lógica de control.

4. Procesador secuencial

4.1. Hasta que no termine de ejecutar una instrucción no comienza a ejecutarse la siguiente

4.2. Procesador monociclo

4.2.1. CPI = 1

4.2.2. La duración de un ciclo de reloj viene fijada por la instrucción de mayor tiempo

4.3. Procesador multiciclo

4.3.1. CPI > 1

4.3.2. La duración del ciclo de reloj es menor que para un monociclo.

4.3.3. Se establece que la duración de un ciclo = duración de la etapa más larga

4.4. Rendimiento:

4.4.1. Fórmula: tiempo de CPU = instrucciones por programa * CPI * tiempo de ciclo

4.5. Tratamiento de Excepciones

4.5.1. consiste en transferir el control a RTE (Rutina de Tratamiento de Excepción ) para qué:

4.5.1.1. Salve el estado del procesador cuando se produzca la excepción

4.5.1.2. Corrija la causa de la excepción

4.5.1.3. Restaure el estado del procesador

4.5.2. Excepción

4.5.2.1. evento no planificado que interrumpe la ejecución de un programa

4.5.3. Interrupción

4.5.3.1. una excepción que proviene de fuera del microprocesador

4.5.4. Tipos de excepciones

4.5.5. Componentes de hardware

4.5.5.1. Registro exception

4.5.5.2. EPC (Contador de programa de excepción)

4.5.5.3. Restador (PC - 4 )

4.5.5.4. cargar en el PC la dirección de memoria donde comienza la RTE

4.5.6. Señales de control

4.5.6.1. ALU_overflow e Ilegal_opcode

4.5.6.2. Exception

4.5.6.3. ExceptionWrite y EPCWrite

4.5.6.4. PCWrite

4.5.7. Modificar la máquina de estados con la que se diseña la unidad de control nanoMIPS multiciclo

5. Procesador monociclo

5.1. nanoMIPS monociclo

5.1.1. Repertorio de Instrucciones

5.1.2. Ruta de datos

5.1.2.1. Componentes

5.1.2.1.1. Memoria de datos

5.1.2.1.2. Memoria de Instrucciones

5.1.2.1.3. 32 registros

5.1.2.1.4. Contador de programa PC

5.1.2.1.5. Dos sumadores

5.1.2.1.6. ALU

5.1.2.1.7. Extensor de signo

5.1.2.1.8. Desplazador a la izquiera

5.1.3. Unidad de control

5.1.3.1. Global

5.1.3.1.1. Decodifica el campo Opcode

5.1.3.1.2. Configuración global de la ruta de datos

5.1.3.1.3. Entrada ← Opcode

5.1.3.1.4. Salidas → Genera los valores adecuados para las diferentes señales de control

5.1.3.2. Local

5.1.3.2.1. Decodifica el campo Funct

5.1.3.2.2. Seleccione la operación que debe realizar la ALU

5.1.3.2.3. Entradas ← ALUOp, Funct

5.1.3.2.4. Salida → Genera la señal ALUControl

5.1.4. Puntos de Control

5.1.4.1. Valores de los puntos de control

5.1.4.1.1. lw

5.1.4.1.2. sw

5.1.4.1.3. ALU

5.1.4.1.4. beq

5.1.5. Ruta de datos + Controlador

6. Procesador multiciclo

6.1. nanoMIPS multiciclo

6.1.1. Adaptación del ciclo de reloj para ejecutar la instrucción más larga

6.1.2. Se reduce el periodo del procesador

6.1.3. Se utiliza una división del trabajo en etapas

6.1.4. Ruta de datos

6.1.4.1. Etapa F

6.1.4.1.1. Registro de instrucción IR

6.1.4.2. Etapa D

6.1.4.2.1. Lectura de operandos A, B

6.1.4.3. Etapa X

6.1.4.3.1. Operandos fuente ALU en A y B

6.1.4.4. Etapa M

6.1.4.4.1. De memoria a MDR

6.1.4.5. Etapa W

6.1.4.5.1. De ALU Out a registro

6.1.4.6. No son necesarios sumadores extra

6.1.4.7. No son necesarias dos memorias separadas

6.1.5. Puntos de Control

6.1.5.1. No se pueden dar como una tabla de verdad

6.1.5.2. Las señales se van modificando en los diferentes ciclos de reloj

6.1.5.2.1. Señales a generar

6.1.6. Unidad de control

6.1.6.1. Global

6.1.6.1.1. Circuito secuencial

6.1.6.1.2. Entrada <- opcode

6.1.6.1.3. Se puede diseñar como máquina de estados o mediante microprograma

6.1.6.2. Local

6.1.6.2.1. De la ALU