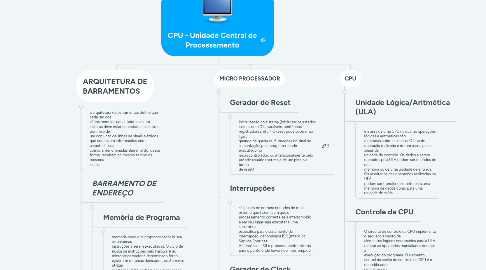

1. ARQUITETURA DE BARRAMENTOS

1.1. a arquitetura de barramentos define que cada um dos vários módulos constituintes de um sistema deve estar conectado aos outros por meio de um conjunto de linhas de sinais elétricos que conduzem informações com características comuns, denominadas Barramento, dessa forma, recebem ao mesmo tempo os mesmos sinais.

1.2. BARRAMENTO DE ENDEREÇO

1.2.1. Memória de Programa

1.2.1.1. memória onde o microprocessador busca as próximas instruções a serem executadas. O ciclo de busca de instruções pelo hardware do microprocessador é denominado fetch cycle. Em sistemas dedicados, costuma-se utilizar memórias ROM, embora em alguns casos memórias RAM também sejam utilizadas (ambas as memórias serão abordadas com mais detalhes a seguir).

1.2.2. Memória de Dados

1.2.2.1. memória onde o microprocessador lê e escreve dados temporários (resultados de operações e cálculos) durante a operação normal. Geralmente é do tipo volátil, embora memórias não voláteis possam ser utilizadas

1.3. BARRAMENTO DE CONTROLE

1.4. Seleção de Endereços e Chip Selects

1.4.1. lógica combinacional para escolher qual memória ou periférico o microprocessador irá utilizar para escrita ou leitura de dados.

2. MICRO PROCESSADOR

2.1. Gerador de Reset

2.1.1. Inicialização do sistema (inicializar os estados iniciais dos I/Os, variáveis, periféricos, registradores, etc.). O reset pode ocorrer ao ligar, quando da queda ou flutuações no sinal de alimentação, pelo programa sendo executado no microcontrolador, ou intencionalmente pelo próprio usuário (por meio de um pino ou botão de reset)

2.2. Interrupções

2.2.1. são sinais de entrada oriundos do meio externo que fazem com que o processamento corrente seja interrompido e em seu lugar seja executada uma sub-rotina específica para o tratamento da interrupção, denominada ISR (Interrupt Service Routine). Ao finalizar a ISR o processamento retorna para o ponto onde havia sido interrompido

2.3. Gerador de Clock

2.3.1. é um circuito eletrônico constituído de um oscilador encarregado de gerar os pulsos digitais necessários à execução e ao sincronismo do sistema. Um sistema computacional é um sistema digital combinacional e sequencial (síncrono e assíncrono), daí a necessidade do gerador de clock (relógio).

3. CPU

3.1. Unidade Lógica/Aritmética (ULA)

3.1.1. é a área de uma CPU na qual as operações lógicas e aritméticas são realizadas sobre os dados. O tipo de operação realizada é determinada pelos sinais da unidade de controle. Os dados a serem operados pela ULA podem ser oriundos de uma memória ou de uma unidade de entrada. Os resultados das operações realizadas na ULA podem ser transferidos tanto para uma memória de dados como para uma unidade de saída.

3.2. Controle da CPU

3.2.1. O circuito de controle da CPU implementa o sequenciamento de elementos lógicos necessários para a ULA realizar as operações requisitadas durante a execução do programa. O elemento central da seção de controle da CPU é o decodificador de instruções.

3.3. Registradores da CPU

3.3.1. Os registradores da CPU são memórias especiais que não fazem parte do mapa de memória. O conjunto de registradores da CPU é frequentemente chamado de modelo de programação.

3.3.1.1. Acumulador ou Registrador A

3.3.1.2. Registrador H:X

3.3.1.3. Registrador Program Counter (PC)

3.3.1.4. registrador Condition Code (CCR)

3.3.1.5. V (Bit de Overflow)

3.3.1.6. H (Bit de Half-carry)

3.3.1.7. I (Máscara de Interrupções)

3.3.1.8. N (Bit Negativo)

3.3.1.9. Z (Bit Zero)

3.3.1.10. C (Bit Carry/Borrow)

3.3.1.11. Stack Pointer (SP)