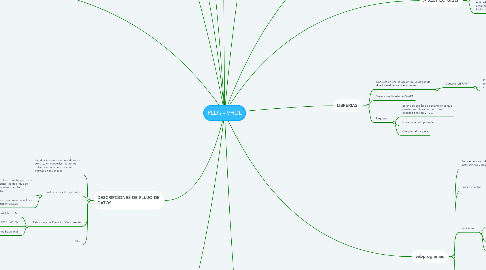

1. TIPO DE DATOS

1.1. ESCALARES

1.1.1. Entero

1.1.2. Real

1.1.3. Enumerados

1.1.4. Boolean

1.1.5. Bit

1.1.6. Fisicos

1.1.7. Character

1.2. TIPOS COMPUESTOS

1.3. SUBTIPOS

1.4. PREDEFINIDOS EN "VHDL"

1.5. NO SOPORTADOS

2. OPERADORES

2.1. LOGICOS

2.1.1. And

2.1.1.1. una puerta lógica digital que implementa la conjunción lógica

2.1.2. Or

2.1.2.1. una puerta lógica digital que implementa la disyunción lógica

2.1.3. Nand

2.1.3.1. es una puerta lógica que produce una salida falsa solamente si todas sus entradas son verdaderas

2.1.4. Nor

2.1.4.1. es una puerta lógica digital que implementa la disyunción lógica negada

2.1.5. Xor

2.1.5.1. una puerta lógica digital que implementa el o exclusivo

2.1.6. Xnor

2.1.6.1. una puerta lógica digital cuya función es la inversa de la puerta OR exclusiva

2.1.7. Not

2.1.7.1. es una puerta lógica que implementa la negación lógica

2.2. Comparación

2.2.1. =

2.2.2. /=

2.2.3. >

2.2.4. <

2.2.5. <=

2.2.6. >=

2.3. Adición

2.3.1. +

2.3.2. -

2.3.3. &

2.4. Multiplicación

2.4.1. *

2.4.2. /

2.4.3. MOD

2.4.4. REM

2.5. Miscelaneos

2.5.1. ABS

2.5.2. **

2.6. Asignación

2.6.1. :=

2.6.2. <=

2.7. Asociación

2.7.1. =>

2.8. Corrimiento

2.8.1. SLL

2.8.2. SRL

2.8.3. SLA

2.8.4. SRA

2.8.5. ROL

2.8.6. ROR

3. DESCRIPCIONES DE FLUJO DE DATOS

3.1. Las descripciones de flujo de datos consiste en especificar como los datos son transferidos de las entradas a las salidas

3.2. Instrucciones Concurrentes

3.2.1. En VHDL todos los bloques son concurrentes, es decir que se están ejecutando en todo momento.

3.2.2. Las instrucciones concurrentes se utilizan fuera de un bloque PROCESS

3.3. Estructuras de Ejecución Concurrente

3.3.1. Asignación condicional WHEN.. ELSE

3.3.2. Asignación WHIT... SELECT... WHEN

3.3.3. Ecuaciones Booleanas

3.4. ALU

4. DESCRIPCIONES COMPORTAMENTALES

4.1. Las descripciones comporta-mentales consiste de una serie de instrucciones, que ejecutadas secuencial-mente, modelan el comportamiento del circuito.

4.2. Instrucciones Secuenciales

4.2.1. Son aquellas que son ejecutadas secuencial-mente, una después de otra.

4.3. Procesos

4.3.1. Es el bloque básico concurrente de ejecución secuencial.

4.3.2. El bloque PROCESS equivale a una sola instrucción concurrente

4.4. Diferencias entre señales y variables

4.4.1. Señales

4.4.1.1. Representa un nodo de conexión entre elementos lógicos (compuertas, registros, buffers, etc)

4.4.1.2. Valor Actual

4.4.1.3. Valor futuro

4.4.1.3.1. Es el que se calcula dentro del proceso, una vez terminado el proceso, los valores futuros de todas las señales se convierten en valores Actuales.

4.4.2. Variables

4.5. Estructuras de Ejecución Secuencial

4.5.1. IF - THEN - ELSE

4.5.2. CASE - WHEN

4.5.3. FOR - LOOP

4.5.4. WHILE - LOOP

4.5.5. WAIT

4.5.5.1. Define implícitamente la lista sensible del proceso

4.5.5.2. WAIT ON

4.5.5.2.1. No es aceptada por la mayoría de las herramientas de síntesis.

4.5.5.3. WAIT UTIL

4.5.5.3.1. Única forma de utilizar WAIT sin tener problemas de síntesis.

4.5.5.4. WAIT FOR

4.5.5.4.1. Se utiliza para simulaciones

5. VHDL

5.1. MULTIPLEXORES

5.1.1. Son circuitos combinacionales con varias entradas y una única salida de datos

5.2. COMPARADORES

5.2.1. apaz de comparar dos señales de entrada y variar la salida en función de cuál es mayor

5.3. ESTILO DE PROGRAMACION "VHDL"

6. IDENTIFICADORES

6.1. Es un conjunto de caracteres que representa diferentes elementos de una descripción.

6.2. Condiciones en VHLD

6.2.1. Permite la utilización de mayúsculas o minúsculas, números y el subrayado (_).

6.2.2. El primer carácter debe ser una letra

6.2.3. El ultimo carácter no puede ser el subrayado, ademas no puede aparecer dos veces o más consecutivas

6.2.4. Mayúsculas y minúsculas son consideradas idénticas; ejemplo Señal_A, señal_a y SEÑAL_A.

6.2.5. Los comentarios en VHDL comienza con dos guiones consecutivos(--)

6.2.6. Existen palabras reservadas, "Palabras Claves", estas no pueden utilizarse como identificadores.

7. OBJETO DE DATOS

7.1. CONSTANTES

7.1.1. Una constante es un elemento que puede tomar un unico valor de un tipo dado.

7.2. VARIABLES

7.2.1. Una variable es como una consante solo tiene un unico cambio la cual es que puede cabliar su valor en cualquier momento

7.3. SEÑALES

7.3.1. Las señales pueden almacenar o pasar valores logicos

7.4. ALIAS

7.4.1. Permite que utilicemos un identificador diferente para hacer referencia a un objeto de datos

8. ATRIBUTOS

8.1. Es una propiedad asociada a señales, entidades o arquitecturas. Se utilizan mediante la camilla simple 'event'.

8.2. un arreglo es un objeto de datos que esta compuesto por varios elementos. Algunos atributos útiles son

8.2.1. 'left': Obtiene el valor que se encuentra a la izquierda de un arreglo.

8.2.2. 'right': Regresa el dato que se encuentra a la derecha del arreglo.

8.2.3. 'high': Permite obtener el mayor elemento de un objeto de arreglo.

8.2.4. 'low': Proporciona el valor mas pequeño del arreglo.

8.2.5. 'lenght': Con este atributo se obtiene el número de elementos de un arreglo

9. ENTIDADES

9.1. Es la abstracción de un circuito, ya sea desde un complejo sistema electrónico hasta una compuerta lógica. Solo describe la forma externa del circuito, se enumeran las entradas y salidas del diseño

9.1.1. Genéricos: Estos son opcionales y se utilizan para declarar propiedades y constantes del circuito. Permiten modelar circuitos en los que podemos cambiar propiedades.

9.1.2. Puertos: Es un objeto de objeto de datos del tipo señal, representa conexiones en el diseño.Lo puertos están asociados a los pines de un símbolo esquemático.

9.1.3. Modos: Indica la forma en que los datos fluyen a través del circuito

9.1.3.1. IN: Describe un pin que únicamente puede ser utilizado como entrada ¿, por que solo podemos leer y nunca escribir sobre el.

9.1.3.2. OUT: Se utiliza para escribir datos pero no para ser leídos

9.1.3.3. INOUT: Indica aquellos puertos que pueden ser utilizados bidireccionalmente.

9.1.3.4. BUFFER: Es utilizado para las salidas que tienen retoalimentación interna.

10. ARQUITECTURAS

10.1. Se utilizan para representar la descripción de un diseño. Describe el funcionamiento de la entidad a la que hace referencia. Una entidad puede tener mas de una arquitectura, pero cuando se compile se indica cual se usará

10.1.1. Descripción del flujo de datos

10.1.2. Descripción Comportamental

10.1.3. Descripción Estructural

11. DESCRIPCIONES ESTRUCTURALES

11.1. Una descripción estructural es similar a un netlist de PSPICE. Son útiles cuando se trata de diseños jerárquicos.

11.2. Componentes

11.2.1. Representa a una entidad declarada en un diseño o libreria.

11.2.2. Declaración de componentes

11.2.2.1. Se realiza dentro de paquetes o en la región declarativa de una arquitectura.

11.2.3. Declaración de componentes con genéricos

11.3. Instanciacion de componentes

11.3.1. Es una instrucción concurrente que especifica la interconexión de las señales del componente dentro del diseño en el que esta siendo utilizado.

11.3.2. Asociación por identificadores

11.3.2.1. En este tipo de instancia es necesario utilizar el operador de asociación => para indicar como se conectan los puertos.

11.3.3. Asociación por identificadores con genéricos

11.3.4. Asociación por posición

11.3.4.1. Solo se colocan las señales, variables o expresiones en el lugar donde deseamos que sean conectadas.

11.3.5. Asociación por posición con genéricos

11.4. Sentencias de Generacion

11.4.1. Permiten crear uno o mas copias de un conjunto de interconexiones.

11.4.2. FOR.. GENERATE

11.4.2.1. Genera un numero finito de conexiones o de instrucciones concurrentes mediante rango discreto.

11.4.3. IF.. GENERATE

11.4.3.1. Realiza la instrucción de instanciación o la instrucción concurrente solo si la condición de prueba es valida.

12. Subprogramas

12.1. Son secuencias independientes de instrucciones y declaraciones.

12.2. Procedimientos

12.2.1. Es un algoritmo que puede regresar uno o varios valores y que, además, puede o no tener parámetros.

12.2.2. Declaración de procedimientos

12.2.2.1. PROCEDURE

12.2.3. Cuerpo del procedimiento

12.3. Funciones

12.3.1. Es un algoritmo que remota un único valor y puede o no tener parámetros de entrada.Generalmente se utilizan para:

12.3.1.1. Convertir objetos de datos de un tipo a otro.

12.3.1.2. Como simples funciones que realizan operaciones para las mas frecuentes situaciones de diseño.

12.3.2. Declaración de funciones

12.3.2.1. FUNCTION

12.3.3. Cuerpo de la función

12.4. Llamado a subprogramas

12.4.1. Cuando el subprograma es llamado cada parámetro recibe un valor. Formas de declarar un parámetro:

12.4.1.1. IN: lectura

12.4.1.2. OUT: escritura

12.4.1.3. INTOUT: lectura y escritura

12.4.1.3.1. Debe ser una variable o señal ya sea para tipos simples como el bit, o arreglos como el bit_vector.

12.4.2. LLamado a procedimientos

12.4.2.1. Se invoca por su nombre, y este utiliza los parámetros que le son listados.

12.4.3. LLamado a funciones

12.4.3.1. Es llamada por su nombre y utiliza los parámetros que le son dados. Las funciones regresan un único valor.

12.4.4. Instrucción return

12.4.4.1. Termina un subprograma. Si el subprograma es una función es necesario utilizar la instrucción return.

12.5. Sobrecarga de operadores

12.5.1. Consiste en definir nuevas funciones para utilizar tipos de datos con los que no estaba definido anteriormente el operador.

13. LÍBRERIAS

13.1. Consiste en una colección de unidades de diseño analizadas previamente.

13.1.1. Clausula: LIBRARY

13.1.1.1. Permite utilizar la librería especificada únicamente para la unidad de diseño en la cual se declara.

13.2. Sintesis de librerias en WARP

13.3. Paquetes

13.3.1. Es una colección de declaraciones que pueden ser utilizadas por otras descripciones en VHDL.

13.3.2. Declaración del paquete

13.3.3. Cuerpo del paquete