1. Diseño de la Jerarquía

1.1. Introducción

1.1.1. Los primeros Modelos de memoria fueron descartados

1.1.2. Existen 3 niveles de memoria: Memoria Cache, Memoria Principal y Memoria Virtual

1.1.3. Cada una: Se ubica en un lugar diferente, se fabrica con una tecnologia diferente y se controla de manera diferente

1.2. Memoria Cache

1.2.1. Ubicada en el procesador

1.2.2. Fabricada con memoria RAM Estatica

1.2.3. Controlado por el controlador de cache

1.3. Memoria Principal

1.3.1. Ubicada en un lugar diferente al procesador

1.3.2. Fabricada con memoria RAM Dinamica

1.3.3. Controlado por el controlador de memoria principal

1.4. Memoria Virtual

1.4.1. Ubicada en el disco duro

1.4.2. Fabricada con tecnologia magnetica

1.4.3. Controlado por el Sistema Operativo

2. Propiedades de una Jerarquía de Memoria

2.1. Inclusion

2.1.1. La informacion de un nivel debe estar tambien en los niveles superiores

2.2. Coherencia

2.2.1. La informacion de un nivel debe ser la misma de los niveles superiores

2.3. Correspondencia de Direcciones

2.3.1. Todas las memorias deben tener correspondencia en las direcciones

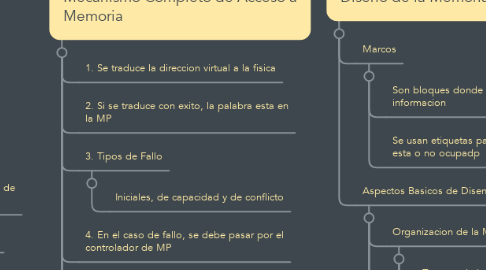

3. Diseño de la Memoria Cache

3.1. Marcos

3.1.1. Son bloques donde se almacena informacion

3.1.2. Se usan etiquetas para verficar si un marco esta o no ocupadp

3.2. Aspectos Basicos de Diseno

3.2.1. Organizacion de la Memoria Cache

3.2.1.1. Tamano de la memoria

3.2.1.2. Tamano del marco

3.2.1.3. Unificacion o division de las instrucciones o datos

3.2.1.4. Implementacion de caches multinivel

3.2.2. Politica de Ubicacion

3.2.2.1. La memoria cache solo almacena algunos bloques de informacion

3.2.2.2. Tipos

3.2.2.2.1. Correspondencia Directa

3.2.2.2.2. Totalmente asociativa

3.2.2.2.3. Asociativa por Conjuntos

3.2.3. Politica de Reemplazo

3.2.3.1. Cuando se produce un fallo en MC se debe determinar el marco a desalojar

3.2.3.2. Se debe tener en cuenta la probabilidad de uso de una pagina y el coste de intercambio

3.2.3.3. Algoritmos utilizados: Aleatorio, FIFO, LRU

3.2.4. Politica de Escritura

3.2.4.1. Toman mucho mas tiempo ya que la escritura no se puede paralelizar

3.2.4.2. Escritura Directa

3.2.4.2.1. Se escribe en el primer nivel de memoria cache y en el siguiente nivel jerarquico

3.2.4.2.2. En caso de fallo, se trae un bloque de MP a MC

3.2.4.2.3. Facil de implementar y asegura la coherencia

3.2.4.2.4. Genera mucho trafico

3.2.4.3. Post-Escritura

3.2.4.3.1. Solo se modifica en el primer nivel de cache

3.2.4.3.2. Para no actualizar la memoria a cada instante se activa un bit sucio

3.2.4.3.3. Menos trafico de informacion y los aciertos se llevan a cabo a la velocidad de la MC

3.2.4.3.4. Diseno mas complejo

3.2.4.3.5. Buffer de Escritura

3.2.4.4. Escritura con Ubicacion

3.2.4.4.1. Se asocia con Post-Escritura y se lleva el bloque de MP a MC

3.2.4.5. Escritura sin Ubicacion

3.2.4.5.1. Se asocia con Escritura Directa y solo se escribe sobre la MP

4. Aciertos y Fallas en el acceso a la memoria Principal

4.1. Cuando una palabra se busca en MC

4.1.1. Si esta, es un acierto

4.1.2. Si no esta, es un fallo

4.1.2.1. La penalizacion dependera del ancho de banda y la latencia de la MP

4.1.2.2. La MC debe cargar el dato de la MP

4.2. Principio de Localidad

4.2.1. Localidad Espacial

4.2.1.1. Si se referencia un elemento, los elementos adyacentes tambien seran refernciados

4.2.2. Localidad Temporal

4.2.2.1. Si se referencia un elemento, tiene una gran posibilidad de volver a ser referenciado

4.3. Lo que pasa entre la MC y la MP tambien puede suceder entre la MP y la MV sin emargo la penalizacion sera mas larga

5. Mecanismo Completo de Acceso a Memoria

5.1. 1. Se traduce la direccion virtual a la fisica

5.2. 2. Si se traduce con exito, la palabra esta en la MP

5.3. 3. Tipos de Fallo

5.3.1. Iniciales, de capacidad y de conflicto

5.4. 4. En el caso de fallo, se debe pasar por el controlador de MP

5.5. 5. El contolador planificara el acceso a MP

5.6. 6. Si acierta, el bloque que contiene la palabra se envia al MC

5.7. 7. En caso de fallo, se debe resolverlo

5.8. 8. El SO realiza un cambio de contexto

5.9. 9. Se lleva el bloque a MC

6. Diseño de la Memoria Principal

6.1. Chips de Memoria

6.2. El controlador de memoria gestiona los accesos

6.3. Mapea la direccion fisica a ubicacion fisica

6.4. Evolucion de las diferentes tecnologias de memoria

6.4.1. DRAM Convencional

6.4.1.1. Proceso de Acceso a memoria

6.4.1.1.1. El procesador vuelca la direccion en el bus, el controlador la decodifica, determina los chips y matrices a ser accedidos y finalmente envia las matrices para validarlas

6.4.1.2. Actualmente obsoleto

6.4.1.3. Se pueden desaprovechar los recursos

6.4.2. Fast Page Mode DRAM

6.4.2.1. Division de la memoria en paginas

6.4.2.2. Los accesos que se encuentran en la misma pagina requieren menos ciclos de acceso

6.4.2.3. Accesos en modo burst, 5-3-3-3, 5 ciclos para el primer acceso y 3 para los siguientes

6.4.3. DRAM Sincronica

6.4.3.1. Utiliza el reloj global del sistema

6.4.3.2. Funciona en modo 5-1-1-1

6.4.3.3. Tiempo de acceso entre 10 y 25 ns

6.4.4. DDR, DDR2 y DDR3

6.4.4.1. Double Data Rate: Transfiere informacion dos veces cada ciclo

6.4.4.2. DDR2 permite trabajar con altas frecuencias

6.4.4.3. A su vez DDR3 tambien aumenta la frecuencia de las 2 anteriores

7. Diseño de la Memoria Virtual

7.1. Memoria Virtual

7.1.1. Permite Multiprogramacion

7.1.2. Permite ejecutar procesos mas grandes que la MP

7.1.3. Permite independencia de las referencias con respecto a la localizacion de los procesos en MP

7.1.4. Es controlado por el SO

7.1.5. Usa almacenamiento magnetico

7.1.6. Se usan paginas en vez de bloques

7.1.7. El alojamiento es asociativo

7.1.8. La politica de escritura es post-escritura

7.2. Mas compleja y dificil de manejar

7.3. Resolver un fallo de pagina implica un cambio de contexto

7.4. Decisiones clave

7.4.1. Tamanio de la pagina

7.4.2. Politicas que reducen el numero de fallos de la pagina

7.4.3. Los fallos de pagina se manejan por software

7.4.4. La escritura directa es descartada

7.5. Organizacion

7.5.1. Direccion Virtual: Direccion otorgada por el procesador

7.5.2. Direccion Fisica: Direccion que maneja la unidad de memoria

7.5.3. Memory Managment Unit: Traduce direcciones virtuales a fisicas y trabaja en tiempo de ejecucion

7.6. Asignacion de Memoria

7.6.1. Paginacion

7.6.2. Segmentacion

7.6.3. Pagina/Segmentada