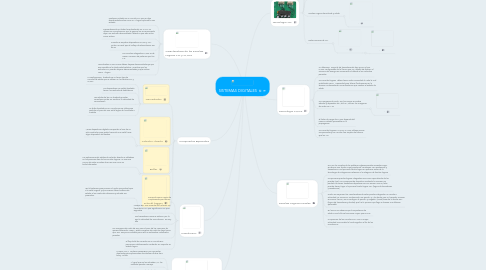

1. Compuertas Especiales

1.1. Tres Estados

1.1.1. La configuracion triestado es un tercer tipo de circuitos de salida que se utilizan en las familias TTL y CMOS

1.1.2. Los dispositivos con salida triestado tienen una entrada de habilitación

1.1.3. Las salidas de los CIs triestado pueden conectarse juntas sin sacrificar la velocidad de conmutacion

1.1.4. Un bufer triestado es un circuito que se utiliza para controlar el paso de una señal logica de la entrada a la salida

1.2. Colector Abierto

1.2.1. Varios dispositivos digitales comparten el uso de un solo conductor para poder transmitir una señal hacia algún dispositivo de destino

1.3. Buffer

1.3.1. Las aplicaciones de salidas de colector abierto se utilizaban en los primeros dias de los circuitos logicos, un uso mas comun de estos circuitos ahora es mas como un bufer/reforzador

1.4. Schmitt trigger

1.4.1. usa la histéresis para prevenir el ruido que podría tapar a la señal original y que causaría falsos cambios de estado si los niveles de referencia y entrada son parecidos.

2. Familia ECL

2.1. Conocida como Lógica de Acoplamiento por Emisor

2.2. La serie ECL mas reciente de Motorola se llama ECLin PS, que significa ECL en pico segundos

2.3. Los transistores nunca se saturan, por lo que la velocidad de conmutación es muy alta

2.4. Los margenes de ruido de ECL para el peor de los casos son de aproximadamente 150mV. Estos margenes de ruido tan bajo hacen que ECL sea poco confiable para usar en ambientes industriales pesados

2.5. El flujo total de corriente en un circuito ECL permanece relativamente constante, sin importar su estado logico

3. Familia BiCMOS de Bajo Voltaje

3.1. La seria 74LVT contiene piezas BiCMOS que están diseñadas para aplicaciones de interfase de bus de 8 bits y 16 bits

3.2. Al igual que en las entradas LVC, las entradas pueden manejar

3.3. Sirven como un traductor de 5v a 3v

3.4. El circuito tiene una realimentación para generar histéresis y así aumentar el márgen de ruido

3.5. Como los niveles de salida [Voh(min) y Vol(max) son equivalentes a los niveles TTL, son totalmente compatibles electricamente

4. Características de las Familias Logicas TTL y CMOS

4.1. Cualquier entrada en un circuito TTL que se deja desconectada actúa como un 1 lógico aplicado a esa entrada

4.2. Frecuentemente no todas las entradas de un CI TTL se utilizan en una aplicación, por lo general no es conveniente dejar una entrada desconectada, debido a que esta actúa como antena

4.3. Cuando se emplean dispositivos CMOS y TTL, juntos, es usual que el voltaje de alimentación sea de 5v

4.4. Los circuitos integrados CMOS es de menor consumo de potencia que los TTL

4.5. Las entradas CMOS nunca deben dejarse desconectadas ya que son sensibles a la electricidad estatica , mientras que las entradas TTL pueden dejarse desconectadas ya que actúan como 1 logico

5. Tecnología TTL

5.1. Lógica de Transistor a Transistor

5.2. Elemento de Entrada y Salida son Bipolares

5.3. Una compuerta NAND TTL estándar disipa una potencia promedio de 10mW

5.4. Niveles Lógicos de Entrada y Salida

5.4.1. .

5.5. Datos Técnicos de TTL

5.5.1. .

5.5.1.1. .

6. Tecnología CMOS

6.1. La utilización conjunta de transistores de tipo pMOS y tipo nMOS configurados de tal forma que, en estado de reposo, el consumo de energía es únicamente el debido a las corrientes parásitas

6.2. Los circuitos lógicos deben tener cierta inmunidad al ruido la cual es definida como "capacidad para tolerar fluctuaciones en la tensión no deseadas en sus entradas sin que cambie el estado de salida

6.3. Los margenes de ruido son los mismo en ambos estados y dependen de Vdd, en Vdd=5v, los margenes de ruido son 1.5v

6.3.1. .