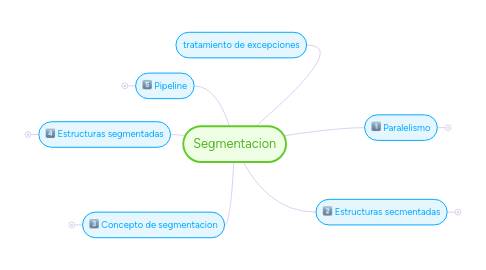

1. Pipeline

1.1. Juego de instrucciones

1.1.1. todas las instrucciones tiene al misma longitud lo que facilita las etapas F y D

1.1.2. MIPS tiene pocos formatos de instrucciones

1.1.3. operandos en memoria solo existen en las instrucciones load/store

1.1.3.1. se puede usar la etapa de ejecución para calcular la dirección de memoria

1.1.4. Los operandos deben estar alineados en memoria

1.1.4.1. por lo q necesita solo acceso a memoria

1.2. relentizacion

1.2.1. resolución de riesgos

1.2.1.1. lo ideal seria mantener todas las etapas del pipeline llenas pero no se da por

1.2.1.1.1. riegos estructurales

1.2.1.1.2. riesgos de datos

1.2.1.1.3. riesgos de control

2. Estructuras segmentadas

2.1. Pipelining Vs Paralelismo

2.1.1. ambas tecnicas estan orientadas a mejorar el rendimiento

2.1.1.1. # instrucciones por unida de tiempo

2.1.1.1.1. Pipelining

2.1.1.1.2. Arquitecturas paralelas

3. Concepto de segmentacion

3.1. conceptos basicos

3.1.1. lo deseanle

3.1.1.1. CPI = 1

3.1.1.2. periodo de reloj limitado por la instrucción mas lenta

3.1.2. la segmentación

3.1.2.1. surge como una técnica para el aumento de prestación

3.1.3. el hardware desaprovecha la mayor parte del tiempo

3.1.3.1. al ejecutar una unica instrucción cada vez

3.1.4. para segmentar el nanoMIPS multiciclo

3.1.4.1. solo se debe comenzar una nueva instrucción cada ciclo

3.1.5. las diferentes instrucciones deben usar diferentes recursos

3.1.5.1. así evitamos conflictos

3.1.6. problemas

3.1.6.1. se realizan accesos a memoria en las etapas F y M

3.1.6.2. Ingresos al banco de registros en las etapas W y D

3.1.6.3. el PC cambia en F

3.1.6.3.1. pero las instrucciones de salto lo pueden modificar en M

3.1.7. soluciones

3.1.7.1. se separan las memorias de instrucciones y las de datos

3.1.7.2. la escritura se realiza en la primera mitad del ciclo y la lectura en la segunda

3.1.7.3. Multiplexor en la etapa F

3.1.7.4. restador en la etapa X

3.1.7.4.1. para realizar al mismo tiempo

3.1.7.5. registros de segmentación

3.1.7.5.1. almacena el resultado de cada etapa al final del ciclo del reloj

3.1.7.5.2. longitud diferente dependiendo de la información que tenga que almacenar

3.1.8. unidad de control del procesador segmentado

3.1.8.1. en la etapa D

3.1.8.1.1. el opcode permite generar todas las señales de control necesarias

3.1.8.2. las señales se propagan por los registros de segmentación

3.1.8.3. tenemos un circuito combinacional que genera señales de control

3.1.8.3.1. para cada tipo de instrucción a partir del opcode

3.1.8.4. dimensionar los registro de segmentación

3.1.8.4.1. X

3.1.8.4.2. M

3.1.8.4.3. W

3.1.9. rendimiento de un procesador segmentado

3.1.9.1. la productividad aumenta

3.1.9.1.1. CPI de un procesador secuencial monociclo

3.1.9.2. el tiempo de ejecución de cada instrucción empeora

3.1.9.2.1. debido al hardware adicional que se introduce

3.1.9.3. speedup

3.1.9.3.1. maximo al segmentar un procesador multiciclo

4. tratamiento de excepciones

5. Paralelismo

5.1. Arquitecturas basadas en Von Nuemann presentan limitaciones tecnicas

5.2. arquitecturas alternativas

5.2.1. usan varias unidades de procesamiento

5.2.1.1. arquitecturas paralelas

5.3. tipos de paralelismo

5.3.1. paralelismo interno

5.3.1.1. unico CPU

5.3.1.1.1. segmentacion

5.3.2. paralelismo explicito

5.3.2.1. varios CPU´s

5.3.2.1.1. SIMD

5.3.2.1.2. MISD

5.3.2.1.3. MIMD

6. Estructuras secmentadas

6.1. Tipos de procesadores

6.1.1. procesadores secuenciales

6.1.1.1. si no termina de ejecutarse una instrucción no empieza otra

6.1.1.1.1. procesador monociclo

6.1.1.1.2. procesador multiciclo

6.1.2. procesadores segmentads

6.1.2.1. permite solapar en el tiempo de ejecución de varias instrucciones

6.1.2.1.1. aprovecha el paralelismo a nivel de instrucción

6.1.2.1.2. es normal q los microprocesadores actuales de proposito general incorporen pipelining

6.2. encauzamiento

6.2.1. técnicas para la generación de paralelismo implícito en computadores

6.2.1.1. ejecución de varias instrucciones usando una única unidad de proceso

6.2.2. la segmentación (pipeline) consiste en dividir una única función en subfunciones independientes

6.2.2.1. distintos procesos a la vez aunq en faces distintas

6.2.3. proceso similar a una cadena de montaje

6.2.3.1. se aceptan nuevos elementos en la entrada antes de que los previamente aceptados salgan x la salida

6.2.3.2. el encauzamiento consigue la ejecución en un tiempo muy inferior a los procesos no encauzados

6.2.4. dividir la etapas de ejecución de las instrucciones en mas etapas

6.2.4.1. el ordenador Strech de IBM

6.2.4.1.1. técnicas de prealimentacion (prefetching)

6.2.4.1.2. dos etapas

6.2.4.2. UNIVAc

6.2.4.2.1. CLAR con 4 etapas

6.2.4.3. Power PC 750

6.2.4.3.1. 6 etapas

6.2.4.4. Motorolo 68040

6.2.4.4.1. 6 etapas