1. Unidad de Control del Procesador Segmentado

1.1. En la etapa D, genera las señales de control necesarias

1.2. Tenemos un circuito combinacional que genera las señales de control para cada tipo de instrucción a partir del opcode

1.3. Dimensionar los registros de segmentación

1.3.1. X

1.3.1.1. ALUSrcA, ALUSrcB, ALUOp y RegDst!

1.3.2. M

1.3.2.1. Branch, MemRead y MemWrite

1.3.3. W

1.3.3.1. MemToReg y RegWrite!

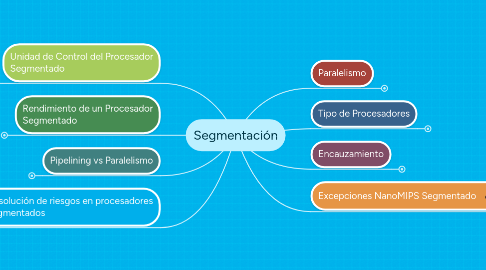

2. Resolución de riesgos en procesadores segmentados

2.1. Riesgos estructurales

2.1.1. Cuando más de 1 instrucción necesita usar el mismo componente de HW al mismo tiempo

2.1.1.1. Resolución

2.1.1.1.1. Duplicar los recursos de HW

2.1.1.1.2. Separar entre memoria de instrucciones y la de datos

2.1.1.1.3. Gestionar el Banco de Registros

2.2. Riesgos de datos

2.2.1. Más de una instrucción presenta dependencias de datos entre sí

2.2.1.1. Tipos

2.2.1.1.1. RAW

2.2.1.1.2. WAR

2.2.1.1.3. WAW

2.2.2. Soluciones

2.2.2.1. SW

2.2.2.1.1. Prevención

2.2.2.2. HW

2.2.2.2.1. Detener el pipeline

2.2.2.2.2. Adenlantamiento o Data fordwarding

2.3. Riesgos de control

2.3.1. Una instrucción que modifica el valor del PC todavía no lo ha hecho cuando se tiene que comenzar la ejecución de la siguiente instrucción

2.3.1.1. Soluciones

2.3.1.1.1. HW Adicional

2.3.1.1.2. Predicción de salto estática

2.3.1.1.3. SW (Compilador)

3. Paralelismo

3.1. Nace por:

3.1.1. Limitaciones en la máquina de Von Neuman

3.2. Tipos

3.2.1. Paralelismo Interno

3.2.1.1. única CPU

3.2.1.2. Segmentación

3.2.2. Paralelismo Explícito

3.2.2.1. Varias CPUs

3.2.2.1.1. SIMD

3.2.2.1.2. MISD

3.2.2.1.3. MIMD

4. Rendimiento de un Procesador Segmentado

4.1. Productividad aumenta

4.1.1. CPI=1

4.2. El tiempo de ejecución de una única instrucción empeora.

4.2.1. Por el Hardware adicional

5. Pipelining vs Paralelismo

5.1. Orientadas a mejorar el rendimiento

5.1.1. Pipelining: El HW no está replicado

5.1.2. Paralelismo: El HW si está replicado

6. Tipo de Procesadores

6.1. Secuenciales

6.1.1. Termina una instrucción empieza otra

6.1.1.1. P. Monociclo

6.1.1.2. P. Multiciclo

6.2. Segmentados

6.2.1. Solapa en el tiempo la ejecución de varias instrucciones

6.2.2. Pipelining (Paralelismo a nivel de instrucción)

7. Encauzamiento

7.1. Es el paralelismo implícito

7.2. Dividir una función en subfunciones independientes

7.3. Consigue la ejecución de instrucciones en un tiempo muy inferior a los procesos no encauzados

8. Excepciones NanoMIPS Segmentado

8.1. Causa de la Excepción

8.1.1. Registro de Excepción

8.1.2. Vector de Interrupciones

8.2. Tipo de Excepción

8.2.1. No Definida

8.2.2. Desbordamiento aritmético

8.3. Características

8.3.1. Se tratan como riesgo de control

8.3.2. Adaptar la ruta de datos para Excepciones

8.4. Trabajo en conjunto del SO y HW

8.4.1. HW

8.4.1.1. Detener la instrucción que provocó el fallo

8.4.1.2. Completar las instrucciones anteriores

8.4.1.3. Vaciar el pipeline de instrucciones posteriores

8.4.1.4. Guardar la causa de la excepción!

8.4.1.5. Salvar la dirección de la instrucción que provocó la excepción

8.4.1.6. Saltar a una dirección predeterminada

8.4.2. SO

8.4.2.1. Cuando se trata de una instrucción indefinida, un fallo hardware o un desbordamiento, el soo mata el proceso y retorna el motivo

8.4.2.2. Cuando se trata de una petición de E/S o de una llamada al sistema, el ssoo salva el estado del programa (cambio de contexto), realiza la tarea en cuestión y, en el futuro, restaura el proceso para que continúe su ejecución .