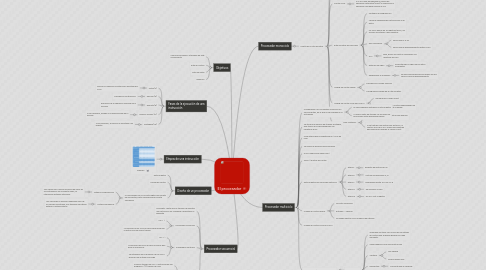

1. Objetivos

1.1. Conocer principios y utilidades de éste componente

1.2. Ruta de control

1.3. Ruta de datos

1.4. Basarnos

2. Fases de la ejecución de una instrucción

2.1. Fetch (F)

2.1.1. Buscar en memoria la instrucción apuntada por el PC.

2.2. Decode (D)

2.2.1. Decodifica la instrucción

2.3. Execute (E)

2.3.1. Ejecución de la operación indicada en el opcode.

2.4. Memory Access (M)

2.4.1. Si es necesario, accede a la memoria para leer o escribir.

2.5. WriteBack (W)

2.5.1. Si es necesario, se vuelca un resultado a un registro

3. Etapas de una instrucción

3.1. Ejemplo

4. Diseño de un procesador

4.1. Ruta de datos

4.2. Unidad de control

4.3. Un procesador es un circuito digital que consta de dos partes, parte combinacional y parte secuencial

4.3.1. Sistema combinacional

4.3.1.1. Sus salidas son función exclusiva del valor de sus entradas en un momento dado, no intervienen estados anteriores.

4.3.2. Sistema secuencial

4.3.2.1. Los valores de la salida no dependen solo de los valores de entrada, sino también del estado anterior o estado interno

5. Procesador secuencial

5.1. Concepto: Hasta que no termine de ejecutar una instrucción no comienza a ejecutarse la siguiente

5.2. Procesador monociclo

5.2.1. CPI = 1

5.2.2. La duración de un ciclo de reloj viene fijada por la instrucción de mayor tiempo

5.3. Procesador multiciclo

5.3.1. CPI > 1

5.3.2. La duración del ciclo de reloj es menor que para un monociclo.

5.3.3. Se establece que la duración de un ciclo = duración de la etapa más larga

5.4. Rendimiento:

5.4.1. Fórmula: tiempo de CPU = instrucciones por programa * CPI * tiempo de ciclo

5.4.2. En el procesador monociclo es un ciclo por instrucción y el tiempo es el tiempo del ciclo más largo

5.4.3. El tiempo del multiciclo es el de la fase que más tiempo toma

6. Procesador monociclo

6.1. Diseño de la ruta de datos

6.1.1. Procesador Monociclo

6.1.1.1. No usar más de una instrucción por recurso cada vez, duplicarlo si es necesario.

6.1.1.2. Se obliga a usar la memoria de instrucciones y datos por separado

6.1.1.3. Añadir multiplexores cuando un valor pueda provenir de varias fuentes.

6.1.2. Control global

6.1.2.1. Para decodificar el campo de código de operación (op)

6.1.3. Control local

6.1.3.1. A la ALU que decodifique el campo de operación aritmética (funct) y seleccione la operación que debe realizar la ALU

6.1.4. Ruta de datos de nanoMips

6.1.4.1. Contador de programa PC

6.1.4.2. Memoria separadas de instrucciones y de datos

6.1.4.3. Un único bando de 32 registros tipo R, de acceso simultáneo a dos registros.

6.1.4.4. Dos sumadores

6.1.4.4.1. Para sumar 4 al PC

6.1.4.4.2. Para sumar el desplazamiento relativo al PC

6.1.4.5. ALU

6.1.4.5.1. BEQ, hacer una resta y comprobar si el resultado es cero.

6.1.4.6. Extensor de signo

6.1.4.6.1. Para extender el signo de los datos inmediatos.

6.1.4.7. Desplazador a la izquiera

6.1.4.7.1. De dos posiciones para recuperar los dos ceros al final de desplazamiento

6.1.5. Unidad de control global

6.1.5.1. Decodifica el campo Opcode

6.1.5.2. Configuración global de la ruta de datos

6.1.6. Unidad de control local para la ALU

6.1.6.1. Decodifica el campo Funct

6.1.6.2. General la señal ALU Control dependiendo de la operación concreta a realizar.

6.1.7. Decodificación multinivel

6.1.7.1. La U.C global decodifica la instrucción leyendo su opcode

6.1.7.2. Si se trata de una instrucción de tipo R, el control local de la ALU realiza una segunda decodificación leyendo el campo Funct.

7. Procesador multiciclo

7.1. Comparando con los diseños monociclo no son eficientes, po lo que no se emplean en la actualidad

7.1.1. Es casi imposible optimizar la ruta de datos

7.1.2. La mayor parte del tiempo los recursos del procesador están desaprovechados

7.2. Se utiliza una división del trabajo en etapas, algo típico de los procesadores con repertorio RISC

7.3. Cada etapa debe completarse en 1 ciclo de reloj

7.4. Se reduce el periodo del procesador

7.5. El CPI medio será mayor que 1

7.6. Tiene 11 puntos de control

7.7. Ruta de datos del nanoMips multiciclo

7.7.1. Etapa F

7.7.1.1. Registro de instrucción IR

7.7.2. Etapa D

7.7.2.1. Lectura de operandos A, B

7.7.3. Etapa X

7.7.3.1. Operandos fuente ALU en A y B

7.7.4. Etapa M

7.7.4.1. De memoria a MDR

7.7.5. Etapa W

7.7.5.1. De ALU Out a registro

7.8. Unidad de control global

7.8.1. Circuito secuencial

7.8.2. Entrada <- opcode

7.8.3. Se puede diseñar como máquina de estados

7.9. Unidad de control local de la ALU

7.10. Unidad de control microprogramada

7.10.1. Memoria ROM

7.10.1.1. Almacena vectores con el valor de las señales de control que se deben generar en cada momento.

7.10.1.2. Cada palabra es una microinstrucción

7.10.1.3. Ventajas

7.10.1.3.1. Más flexible

7.10.1.3.2. Ocupa menos área

7.10.1.4. Desventaja

7.10.1.4.1. Más lenta que la cableada

7.10.1.5. Condificación horizontal

7.10.1.5.1. Cada microinstrucción incorpora directamente los valores que deben tomar las señales de control.

7.10.1.6. Codificación vertical

7.10.1.6.1. Se evita que sean demasiado largas, las microinstrucciones se codifican

7.10.1.6.2. Se necesita un paso previo paso de decodificación

7.10.1.6.3. A éstos campos se les añade la etiqueta de la microinstrucción y la información de secuencia